Description: Cadence (NASDAQ:CDNS) provides software and hardware design tools, intellectual property, and verification services to semiconductor firms (60% revenues) and system companies (40% revenues).

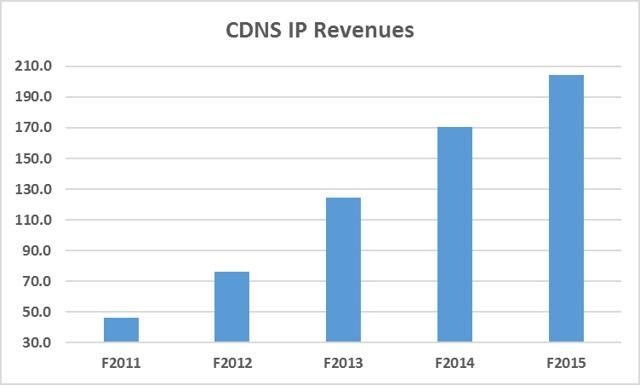

Investment Thesis: Cadence is a high-margin (89% Gross Margins) "subscription software" company with strong revenue predictability and a long-term ratable business model, currently trading at low hardware-like multiples. The Electronic Design Automation (EDA) industry has consolidated into an oligopoly with three main players, outperforming the semiconductor sector over the past decade. The business is characterized by high margins, strong free cash flow, high barriers to entry, and low capital intensity levels. CDNS is a 20% FCF margin business, with Net Income to FCF conversion > 100%. It grew FCF 20% in 2015, and has guided to 20% growth (conservative) again this year. Stock is trading at 4.8% TTM FCF yield, growing to 6.8% yield for FY17. Cadence's licensing business is a hidden asset, having grown at a >40% CAGR from $50M to >$200M in revenues last 5 years. Our work suggests M&A-driven R&D headwind concerns are overblown. Indeed, 40-50% revenues are from system companies (e.g Alphabet, Apple, etc.); 7-8% revenues/bookings growth in 2015 against a backdrop of negative industry growth rates proves the resiliency in business model.

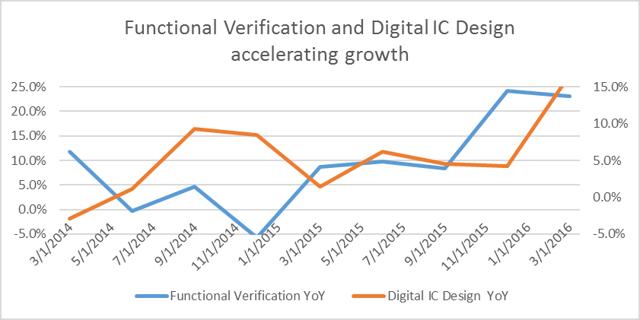

Catalysts: Immediate catalysts include strong growth in Digital IC (up 17% YoY FY16 Q1) and Functional Verification (emulation) (up 23% YoY FY16 Q1) categories driven by new product cycles, cyclical re-acceleration in semiconductor growth, and a $720M buyback shrinking share count by 10.5% YoY (vs. 4% and 2% dilution in 2014 and 2015). This compares favorably to 2014 and 2015, when share count went up 5.4% (despite $430M share buyback) due to equity dilution to warrant and convertible note holders (notes expired in 2015).

EDA Sector

The EDA sector has poor sell-side analyst coverage and general investor apathy due to the high technical complexity of the industry involved. This is a high quality collection of software businesses with high market share and high switching costs. The sticky user base is due to productivity losses incurred in learning new tools. (If a start-up introduced a new Excel competitor but you couldn't use your macros or keyboard shortcuts, and with possible compatibility issues with older files, would you switch to save costs?)

Given current valuation, stock is pricing in modest growth with M&A headwinds, but not the optionality of strong appreciation should cyclical industry growth resume. Given the high FCF and stable business attributes, the business is also a great candidate for M&A or PE takeover.

Company Description

Cadence provides hardware and software design tools and verification services as well as intellectual property (IP) blocks to semiconductor firms. Some of Cadence's products are the solutions of choice for their end markets: Virtuoso for analog, Jasper for formal (equivalence) verification, and Palladium for emulation. Other names include Innovus, Encounter, Tensilica, Voltus, Allegro, etc.

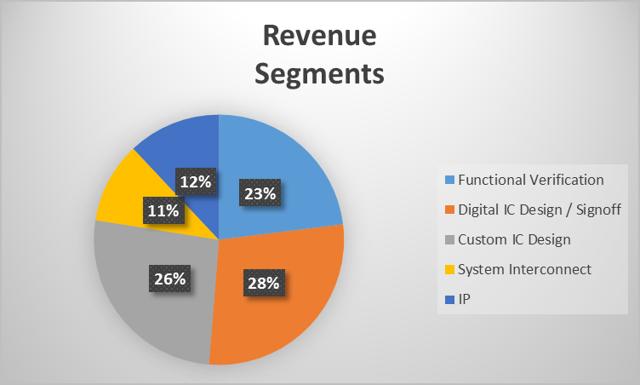

Figure 1: Cadence Geographic and Revenue mix (2015 Revenues)

The revenue and geographic mix for Cadence is given above. Cadence's core strength has been Custom IC Design (up 74% 2011-2015) and Interconnect (up 78% 2011-2015). Japan revenues were down 21% from 2011-2015 due to FX and cyclical headwinds, but have started growing again recently.

Investment Thesis

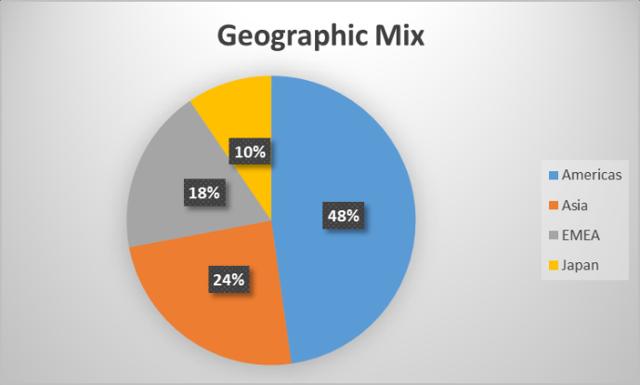

1. The EDA Industry is an Oligopoly with strong pricing strength: The Electronic Design Automation (EDA) industry has consolidated through M&A into three main players (Synopsis, Cadence, Mentor Graphics), resulting in pricing power and has outperformed the semiconductor industry over the last decade. In fact, Mentor is a much smaller player and uncompetitive in several sectors. Moreover, within EDA sub-verticals, each company has a dominant market share. This slide from 2011 shows that the #1 supplier in each EDA product segment averages 66% market share. The industry has further consolidated since that time.

Figure 2: EDA sub-segments and market share (Source: Mentor Graphics)

We expect EDA's share of semiconductor revenues to continue to rise, after declining for almost a decade. The industry thus faces a favorable pricing environment. We have heard some contract renewals being negotiated at 25% higher price; industry clearly believes there's value to be captured.

2. Growth should reaccelerate: Optically, Cadence's revenue growth has been deaccelerating due to end-markets and product cycle related headwinds. We believe growth will accelerate from here. Our rough math (assuming 40% incremental operating income) suggests every 100 bps uptick in organic growth to be worth $0.03 in incremental EPS.

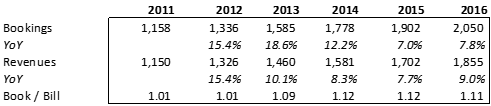

In a backdrop of a semiconductor industry with negative growth in 2015, Cadence grew revenues 7.7% and bookings 7%. As we get a cyclical upturn in various end-markets, Cadence could easily hit mid-teens revenue growth (average from 2012-2014), especially when we consider share gains in emulation and digital IC design tools.

Figure 3: Cadence Bookings and Revenues

While the 2015 industry unit-growth of 10% was similar to 2014, the revenue growth was masked by FX headwinds. With automotive content growth, replacement demand in mobile and PCs, consumer growth in emerging markets, we believe semiconductors should deliver 3-4% revenue growth over the next 3-5 years. This is not factoring in any growth in EDA spend from the rising demand from Chinese semiconductor firms.

3. R&D M&A headwind concerns overdone: Over the years, there have been a number of secular concerns that have turned out untrue for the overall growth of the EDA industry. First, there was the concern of "secular trend" towards the usage of "programmable chips" (i.e. FPGAs) vs. ASICs. The second concern was R&D spend shifting towards Asia with patchy record of intellectual property enforcement. Moreover, there was concern about round-the-clock R&D effort reducing the number of licenses needed for simultaneous users.

The latest concern is US semiconductor M&A impacting R&D spending which hurts EDA spend. If you look at the big M&A announced last year, the estimated impact of R&D cuts would be <2% of total R&D. Further, 40% of Cadence revenues are from non-semiconductor system companies. Thus, the actual headwind for CDNS should be roughly 1% from M&A.

To better understand the unit economics behind R&D, we believe it is imperative to understand two main drivers behind R&D spend. First is the per-seat R&D spend to enable productive engineering resources. Second is the aggregate R&D spend driven by new chip-design activities on tools, masks, computing resources, etc. (So if on aggregate a new chip costs $20M in R&D, it is largely this expense we are talking about.) Given our view that engineers will largely remain in demand and employed, the first should remain sticky, while the second will face headwinds. Cadence, largely due to its strength in analog, is more levered to the first trend, and Synopsys (SNPS) to the second. We like this cyclical resiliency.

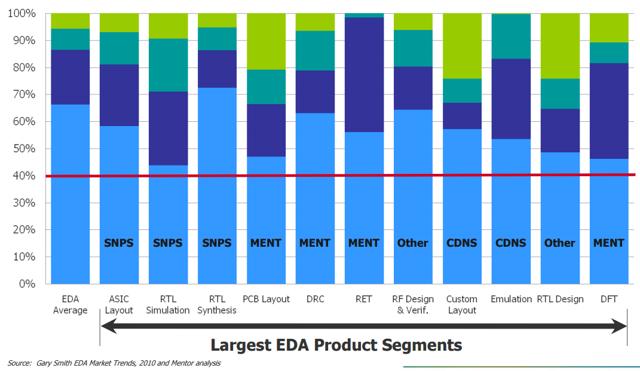

Rising complexity has driven higher spend, largely on masks, tools and services.

Figure 4: Design costs rising rapidly (Source: IHS)

4. Functional Verification (Emulation) and Digital IC Segment (55% Revs) growth rates accelerating:

Figure 5: Functional Verification and Digital IC Design Segments (55% Revs) Growth YoY%

Functional verification segment includes design and verification building blocks which Cadence provides and are used to accelerate design cycles. It also includes Palladium, Cadence's hardware-based verification solution (emulation). Emulation is a technology used by chip companies to verify that their chips work in the context of the system and software that they would be designed into. Cadence is an emulation leader and its emulation solution (Palladium) is a jewel in its product suite. It has a new product, Palladium 2, whose refresh should drive a product cycle in this category.

While street is fixated on M&A curtailing R&D spend, we believe emulation spend would be driven by growth vectors like virtual reality, gaming, GPUs, computer vision and ADAS; all computationally intensive end-markets where emulation has historically proven its time-to-market advantages. A random search for emulation job listings in the Bay Area shows companies like Apple, Intel, Xilinx and Broadcom investing heavily in their respective emulation efforts.

Digital IC Design: We believe that Cadence is gaining share in digital (currently a Synopsys stronghold) due to new products and management. The new SVP, Anirudh Devgan, is a known industry veteran, and has helped CDNS launch new products (Tempus, Voltus, Quantus, Innovus) to explicitly target and grow market-share in this category, as can be seen from recent growth rates.

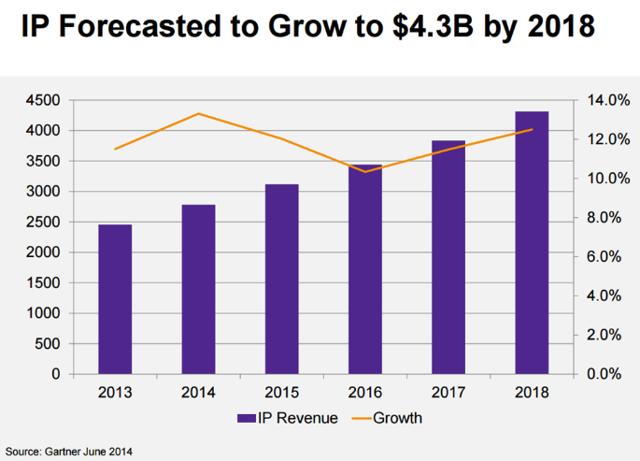

5. Intellectual Property segment is a hidden asset: Cadence is the fourth largest Intellectual Property provider after ARM (ARM), Imagination (IGNMF) and Synopsys. It has made strategic acquisitions like Denali and Tensilica and is currently the dominant provider of several important IP blocks used in a system-on-chip. Licensing and royalty businesses are pure-profit businesses and are valued at very high multiples in the market. Licensing business has grown from $50M run-rate to a >$200M annual revenue business.

Both Synopsys and Cadence have targeted low double-digit growth for this segment (though last couple of quarters have been slow for Cadence).

Figure 6: Gartner IP Growth forecast; CDNS IP Revenues

6. Dominant position in Custom IC Design (analog): The Custom Design tool segment consists of analog tools and the company's platform (Virtuoso) is the dominant industry standard in this segment. Cadence has been an industry leader in providing analog design tools. It has a large captive analog engineering design community who has learned design using Cadence tools. There is an enormous switching cost involved for companies and employees, and Cadence tools thus tend to be very sticky. Cadence has been using its analog strength to cross sell other products as well (through an "integrated flow" and other such bundled features).

7. Share count dilution headwinds due to dilutive convertible notes are past: Cadence issued convertible notes due in 2013 ($144M) and 2015 ($350M). It also entered into a separate warrant transaction (2015 Warrants) for purchase of 46.8M shares at $10.78 per share. Due to these warrants, Cadence issued 23.1M shares of common stock to the 2015 Warrant counter parties. These were highly dilutive to share count; despite buying back $430M worth of stock in FY2014 and FY2015, share count went up by 5.4% over the period. They were thus a terrible drain on cash flow with no real return to shareholders. Going forward, we don't see any further dilution except the stock-based compensation dilution of ~1.5%/year. Cadence has $720M in share buybacks remaining; current share-count guide for FY16 implies a 10.5% YoY reduction in float.

8. Turnaround story with expanding margins: Lip Bu Tan, the Cadence CEO, has been a venture capitalist for almost 30 years. Appointed in 2010, the new management moved Cadence to a long-term ratable business model with strong predictability and pricing discipline in their revenue streams. With 3-4% semiconductor industry growth rates, 2%/year EDA share gain and a 1-1.5% Cadence turnaround growth rate, Cadence should grow revenues by at least 7-8%.

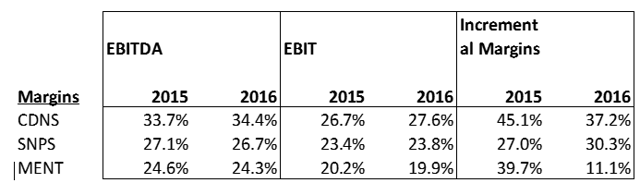

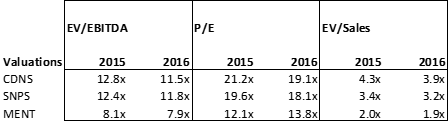

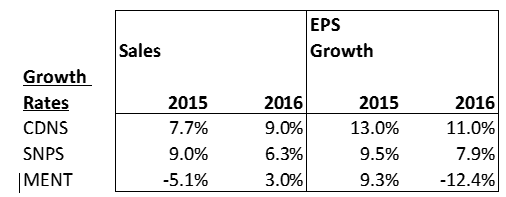

9. Comparative analysis between Cadence, Synopsys and Mentor Graphics Favors Cadence

Mentor: We believe Mentor (MENT) is a sub-scale competitor to both Cadence and Synopsys; primarily a monopoly on the digital implementation tool Caliber. There might be a take-out value to Mentor (i.e. Icahn), but we believe that is fairly well known. Mentor screens cheap on valuation metrics, but it's a lower quality name.

Synopsys: Synopsys is a worthy competitor to Cadence, with potentially higher share of high-margin, low capital intensity businesses like IP licensing. We find Cadence's analog products to be stickier based on strong product preferences. Secondly, any R&D headwind should first manifest itself in fewer new design activities and fewer tape-outs. Synopsys, through products like Design Compiler and Prime-Time, is more levered to chip tape-out activities and should thus face stronger headwinds should M&A lower new chip design activity. We also believe Cadence is a more catalyst-rich name at these levels for reasons mentioned elsewhere. Finally, with 60% revenues from Digital IC Design ($1.35B), Synopsys has a lot more to lose in terms of market share loss.

Interestingly, Synopsys and ARM are the two biggest vendors in intellectual property and compete aggressively against each other. This naturally results in closer partnerships between ARM and Cadence, and a desire on the part of ARM to help Cadence succeed.

Cadence is slightly more expensive to Synopsys:

But, it has had better margins, better growth rates and, importantly, higher incremental margins as well.

Figure 7: CDNS, MENT SNPS Margins, Valuations, Growth Rates

We only need to look at the gross and operating margin improvements to see that Cadence has been the biggest beneficiary of the industry consolidation and technology trends discussed here. CDNS has gone from below average gross and operating margins to leading margins in a span of 5-7 years.

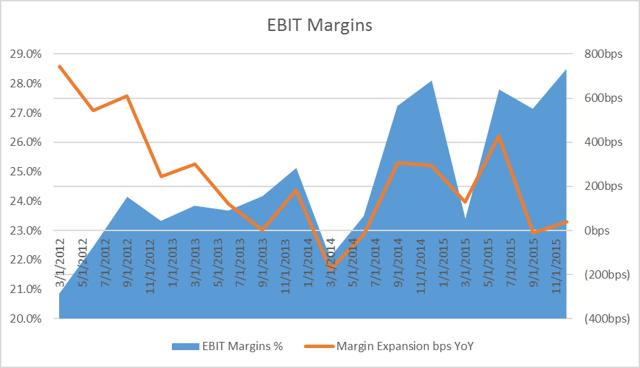

Steady EBIT margin expansion over the last 5 years as business model shows operating leverage:

Figure 8: CDNS EBIT Margins and YoY Change (2012-2016)

Valuation and stock drivers

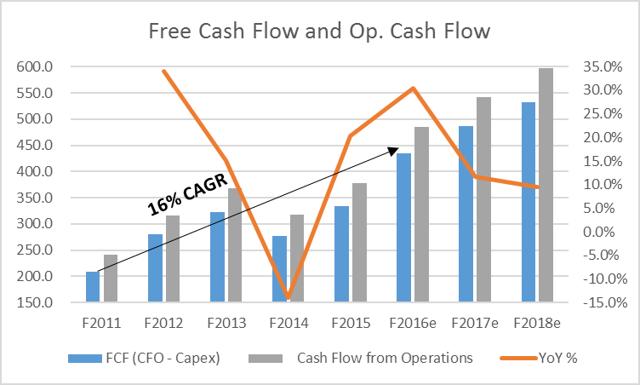

Cadence screens cheap on FCF yield basis vs. historical range. Management guide for Operating Cash Flow implies 20% FCF growth in 2016; we believe they will easily exceed that number.

Figure 13: CDNS FCF and CFO (2011-2016)

We feel the stock is worth $29, or 17x FY17 EPS of $1.60 plus cash.

Misc. Factors

The rise of vertically integrated silicon providers and IP reuse: Technology companies like Apple, Alphabet, Microsoft and Oracle are vertically integrating and increasingly designing their own chips as a product differentiation strategy. This represents a new and growing source of revenues for Cadence.

Expansion into adjacent markets: A number of these tools are "checklist" tools that qualify code, product or designs towards certain quality levels early in the design process. Leveraging common R&D and sales channel resources, these can potentially be used in adjacent markets. Indeed, Synopsys has expanded into security software, Mentor Graphics into transportation and automotive, and Cadence into Aerospace designs.

Moore-stress could lower R&D intensity levels: Cadence has grown R&D expenses by 50% last 3 years and R&D intensity levels to 38% of revenues. Any reduction in R&D intensity levels due to Moore stress and slower technology node transitions will drive margin expansion and higher profitability.

Investment risks

- Lower organic growth due to lower R&D spend: Clearly, R&D spend can become a headwind should our assumptions on revenue headwinds prove to be low.

- Share loss in Emulation and Digital due to competitor product cycle: Cadence has recently gained share and any reversal resulting in share loss would be a set-back.

- New CFO resets earnings expectations lower, resulting in share underperformance: Cadence CFO Geoff Ribar is retiring March 2017. A new CFO could bring his own set of ideas on capital allocation and business execution.

- Higher than expected ramp in spending (R&D) to support new end-markets or technology nodes.